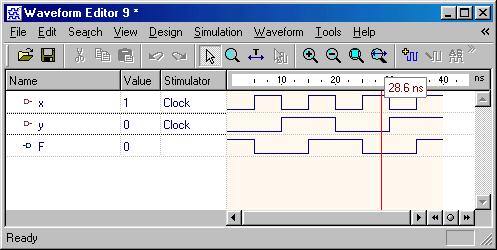

DUT Instantiation // : FPga projects, Verilog projects, VHDL projectsĭata_out, fifo_full, fifo_empty, fifo_threshold, fifo_overflow,Įnd // 9. Parameter definitions parameter ENDTIME = 40000 Include Statements //`include "counter_define.h" module tb_fifo_32 Preprocessor Directives `define DELAY 10 // 3. : FPga projects, Verilog projects, VHDL projects // Verilog project: Verilog code for FIFO memory // Verilog Testbench code for FIFO memory // 2. The timescale directive `timescale 10 ps / 10 ps Reg fifo_full, fifo_empty, fifo_threshold, fifo_overflow, fifo_underflow Īssign pointer_equal = (wptr - rptr) ? 0 : 1 Īssign pointer_result = wptr - rptr įifo_empty = ( ~fbit_comp) & pointer_equal įifo_threshold = (pointer_result ||pointer_result) ? 1 : 0 Įnd always posedge clk or negedge rst_n)Įlse if((overflow_set = 1) &(fifo_rd = 0))Įlse if((underflow_set = 1) &(fifo_we = 0))Įnd endmodule // : FPga projects, Verilog projects, VHDL projects // Verilog project: Verilog code for FIFO memory // Verilog code for Write Pointer sub-module module write_pointer(wptr,fifo_we,wr,fifo_full,clk,rst_n) Įnd endmodule Verilog testbench for the FIFO memory: Wire fbit_comp, overflow_set, underflow_set Input wr, rd, fifo_we, fifo_rd,clk,rst_n Status_signal top4(fifo_full, fifo_empty, fifo_threshold, fifo_overflow, fifo_underflow, wr, rd, fifo_we, fifo_rd, wptr,rptr,clk,rst_n) Įndmodule // : FPga projects, Verilog projects, VHDL projects // Verilog project: Verilog code for FIFO memory // Verilog code for Memory Array submodule module memory_array(data_out, data_in, clk,fifo_we, wptr,rptr) Įnd assign data_out = data_out2] Įndmodule // : FPga projects, Verilog projects, VHDL projects // Verilog project: Verilog code for FIFO memory // Verilog code for Read Pointer sub-module module read_pointer(rptr,fifo_rd,rd,fifo_empty,clk,rst_n) Įnd endmodule // : FPga projects, Verilog projects, VHDL projects // Verilog project: Verilog code for FIFO memory // Verilog code for Status Signals sub-module module status_signal(fifo_full, fifo_empty, fifo_threshold, fifo_overflow, fifo_underflow, wr, rd, fifo_we, fifo_rd, wptr,rptr,clk,rst_n) Memory_array top3(data_out, data_in, clk,fifo_we, wptr,rptr) Read_pointer top2(rptr,fifo_rd,rd,fifo_empty,clk,rst_n) Write_pointer top1(wptr,fifo_we,wr,fifo_full,clk,rst_n) Output fifo_full, fifo_empty, fifo_threshold, fifo_overflow, fifo_underflow Input data_in // FPGA projects using Verilog/ VHDL output data_out : FPga projects, Verilog projects, VHDL projects // Verilog project: Verilog code for FIFO memory // Top level Verilog code for FIFO Memory module fifo_mem(data_out,fifo_full, fifo_empty, fifo_threshold, fifo_overflow, fifo_underflow,clk, rst_n, wr, rd, data_in)

0 kommentar(er)

0 kommentar(er)